Chipset kryptograficzny obsługuje ruch SSL

-

- NetWorld,

- 04.10.2002

Secure Sockets Layer (SSL) to standardowa metoda zabezpieczania transakcji webowych. Obliczenia konieczne przy kryptografii SSL dotyczą bardzo wielkich liczb i skomplikowanych funkcji matematycznych nie zawartych w zestawach instrukcji większości komercyjnych procesorów.

Secure Sockets Layer (SSL) to standardowa metoda zabezpieczania transakcji webowych. Obliczenia konieczne przy kryptografii SSL dotyczą bardzo wielkich liczb i skomplikowanych funkcji matematycznych nie zawartych w zestawach instrukcji większości komercyjnych procesorów.

Sprzętowa obsługa SSl

Na ogół rozwiązuje się ten problem przez dokupienie serwerów z wieloma procesorami do obsługi bezpiecznych połączeń, w tym krytycznego zestawu transakcji, takich jak wymiana numerów kart kredytowych.

Alternatywnym rozwiązaniem jest przyspieszenie kryptografii SSL przez zastosowanie koprocesorów. Takie układy - przeprowadzające szyfrowanie RSA, szyfrowanie masy danych (bulk data) lub oba naraz - nadal jednak zależą od głównego procesora przy otrzymywaniu i wysyłaniu rekordów SSL do układu kryptograficznego.

Przetwarzają one do tysiąca żądań potwierdzenia (handshake) SSL na sekundę. Jednakże ich stosowanie wymaga elementu spajającego, zapewniającego sprawną współpracę pomiędzy układem kryptograficznym a głównym procesorem. Poza tym rozwiązanie to w dużej mierze jest zależne od szyny PCI (albo PCI-X) przy przekazywaniu danych pomiędzy układem kryptograficznym a głównym procesorem. Taka architektura zwiększa złożoność i tworzy wydajnościowe wąskie gardła, ponieważ do przeprowadzenia nawet jednej sesji potwierdzenia SSL potrzebna jest wielokrotna wymiana danych pomiędzy koprocesorem a głównym CPU.

System w chipsecie

Dlatego rozwiązaniem może być umieszczenie całego systemu w jednym układzie, który przeprowadzałby klasyfikację ruchu, kompletne szyfrowanie z protokołem SSL i szyfrowanie masy danych.

Takie rozwiązanie eliminuje całkowicie interakcję z głównym procesorem, jest mniej skomplikowane i zwiększa wydajność systemu. Chipset z procesorem zapewnia standardowy interfejs Gigabit Ethernet dla klienta i serwera.

Jednym z największych obciążeń w przetwarzaniu wielkiej liczby sesji SSL jest przetwarzanie pakietów TCP/IP z zakapsułkowanymi rekordami SSL. Już zwykły gigabitowy ruch TCP/IP może przeciążyć typowy CPU, a co dopiero sesje SSL.

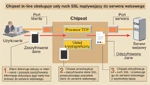

Nowy chipset ma zintegrowany wydajny procesor, który przetwarzając ruch SSL obsługuje segmentację TCP, szeregowanie pakietów i inne funkcje protokołowe, mogące "zamęczyć" host. Interfejs strony klienta to port GMII (Gigabit Media Independent Interface), który powinien być ulokowany bezpośrednio za kartą sieciową (NIC) lub fizycznym interfejsem urządzenia.

Kliencki ruch HTTP przechodzi bezpośrednio przez chipset do portu serwera, także z interfejsem GMII. Wchodzący ruch SSL jest kierowany do części kryptograficznej chipsetu, obsługującego wszystkie funkcje protokołowe SSL i szyfrowania masy danych oraz porządkującego rezultat działania, czyli komunikaty tekstowe, przed przekazaniem ich do portu serwera.

Najważniejsze jest porządkowanie

Docelowy serwer będzie uwolniony od spadku wydajności związanego z przetwarzaniem ruchu SSL i będzie sobie lepiej radził z transakcjami SSL - z powodu uporządkowanej natury przekazywanych mu pakietów TCP/IP.

Jednak opisywane rozwiązanie nie będzie przydatne, jeśli nie będzie wykonywało wszystkich sieciowych i kryptograficznych funkcji z pełną szybkością łącza - do 1 Gb/s, w trybie dupleksu. Przekłada się to na wydajność rzędu 100 000 obsłużonych zadań potwierdzenia SSL na sekundę.

Konfiguracja, ładowanie klucza SSL, plików certyfikujących oraz informacji zarządzających są przeprowadzane przez port zarządzania z interfejsem GMII. Wszystkie funkcje zarządzające i komunikacja mogą być chronione przez SSL.

Potrzeba chronienia coraz większej części ruchu sieciowego i osiąganie przy tym wydajności wynikającej z szybkości łącza wymuszają nowe podejście do technik kryptograficznych. Zarządzalne i wydajne rozwiązanie z chipsetem in-line może być łatwo integrowane z kartami sieciowymi serwerów webowych, specjalizowanych urządzeń serwerowych i innego sprzętu działającego w warstwach 4 - 7 modelu OSI.