MIT prezentuje eksperymentalny układ CPU zawierający mini-routery

-

- Janusz Chustecki,

- 25.06.2014, godz. 14:28

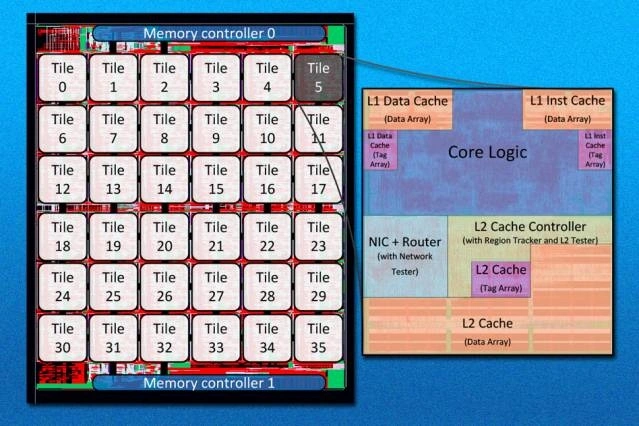

Naukowcy z MIT (Massachusetts Institute of Technology) zaprojektowali 36-rdzeniowy procesor, którego cechą jest to, że rdzenie wymieniają dane z buforem w specyficzny, koherentny sposób. Dzięki temu procesor jest w stanie wykonać powierzone mu zadanie wykorzystując dużo mniejszą liczbę cykli obliczeniowych, niż ma to miejsce w klasycznych układach CPU.

Naukowcy zagnieździli w układzie mini-routery, które zawiadują danymi wymienianymi między rdzeniami i buforem pamięci. W efekcie operacja przesyłania danych między tymi elementami układu przebiega szybciej, co bezpośrednio przekłada się na wzrost wydajności układu. Badania wykazały, że procesor mający taką architekturę nadaje się wyjątkowo dobrze do obsługiwania aplikacji, w których wiele zadań można wykonywać równolegle. Są to np. aplikacje analizujące dane finansowe, czy symulujące różnego rodzaju zjawiska fizyczne.

Twórcy procesora nadali zastosowanej w nim technologii nazwę "shadow network". Duże porcje danych odbierane przez układ są dzielone na mniejsze części, które są następnie rozsyłane przez mini-routery do poszczególnych rdzeni. Każdy z rdzeni ma do dyspozycji własny bufor pamięci, w którym przechowuje dane. Ważne jest to, że rdzeń może pobierać dane zarówno z tego bufora, ja i z pozostałych buforów rozsyłając żądanie dostępu (broadcast). Jest to możliwe właśnie dzięki mini-routerom i specyficznego rodzaju mini-sieci LAN (“shadow network”) zagnieżdżonej na układzie.

Zobacz również:

- Sztuczna inteligencja od Apple wymagać może nowych procesorów

- Nabór do nowej edycji programu akceleracyjnego StartSmart CEE

Architektura układu

Przeprowadzone analizy wykazały, że 36-rdzeniowy układ CPU bazujący na technologii “shadow network” pracuje o 24,1% szybciej od klasycznych układów CPU dysponujących taką samą ilością rdzeni obliczeniowych. Prototypowy układ został wyprodukowany przez firmę Freescale Semiconductor przy użyciu technologii 45 nanometrów. Zachęceni wynikami testów naukowcy zamierzają zaprojektować układ zawierający kilkaset rdzeni i sprawdzić, czy opracowana technologia również wtedy okaże się efektywna.

Dokładna specyfikacja techniczna układu została zaprezentowana niedawno w Minneapolis (USA) na konferencji International Symposium on Computer Architecture.